# **IQS7221G DATASHEET**

On-Axis Hall-Rotation Sensor With Adjustable Interval UI, Quadrature, Freewheel UI, Two Inductive/Capacitive Channels, and Haptic Interface

### 1 Device Overview

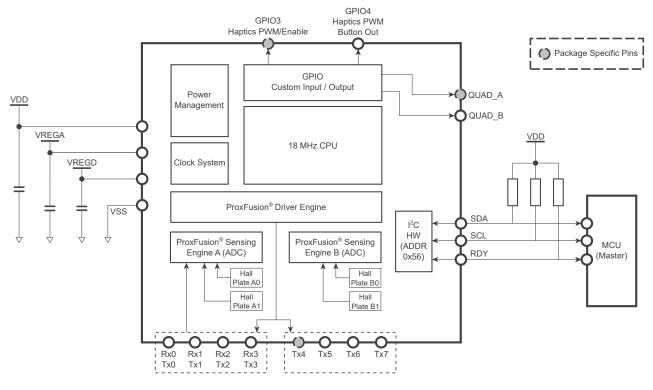

The IQS7221G ProxFusion<sup>®</sup> IC is a sensor fusion device for rotation and angle sensing applications using a diametrically-polarised magnet in an on-axis configuration. Two ProxFusion<sup>®</sup> channels are included for integrated UI applications. The dedicated quadrature outputs make the product a drop-in replacement for mechanical and optical rotary encoders. The IQS7221G includes a virtual freewheel UI for more intuitive scrolling, and a haptic waveform generator to provide haptic feedback with an LRA via a compatible H-bridge.

#### 1.1 Main Features

- > Highly Flexible ProxFusion<sup>®</sup> Device

- > Hall-Effect Angle Sensor

- 4 Hall plates

- On-axis orientation

- 16-bit absolute angle output

- <1° angle error<sup>i</sup>

- Wide operational range

- Automatic Tuning Implementation (ATI)

- Automatic synchronisation with mechanical ratchets

- > Two ProxFusion<sup>®</sup> channels

- Supports self-capacitance, mutual-capacitance, or inductive sensing

- Automatic Tuning Implementation (ATI)

- Button UI to detect large changes

- Movement UI to detect small/rapid changes

- Integrates with Hall angle sensor for virtual freewheel UI

- > Interval UI

- Configurable number of intervals per rotation

- Configurable hysteresis between intervals

- > Virtual Freewheel/Hyperscroll UI

- Integrates the ProxFusion<sup>®</sup> Movement UI with the Hall sensor to detect "flick" gestures

- Emulates a freely-spinning wheel adds hyperscroll functionality to devices without expensive mechanical assemblies

- > Haptic Waveform Generator

- Generate PWM waveforms to drive a Linear Resonant Actuator (LRA) through an H-bridge

- Automatically trigger a haptic event on interval change or ProxFusion® button activation

- > Standalone Mode

- Quadrature outputs indicate interval change and direction

- GPIO output to indicate button press on one of the ProxFusion<sup>®</sup> channels (incompatible with Haptic UI)

- > I<sup>2</sup>C Interface With IRQ/RDY Signal

- > Design Simplicity

- PC software for configuration and debugging

- Guidelines for magnet selection and mechanical constraints

- > Supply Voltage: 1.8 V to 3.6 V

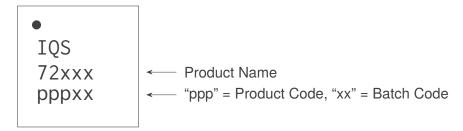

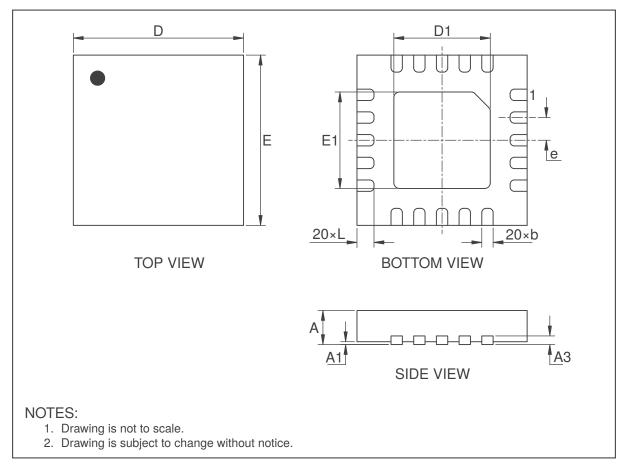

QFN20 Package

Dependent on magnet alignment and mechanical tolerances

- > Small Package

- QFN20 (3 × 3 × 0.5 mm) 0.4 mm pitch

### 1.2 Applications

- > Scroll-wheels for computer peripherals

- > Mouse wheels

- > Applications requiring flexible UI options with sensor fusion

- > Mechanical and optical rotary encoder replacements

- > Adjustment and control knobs

- > Motor encoders

### 1.3 Block Diagram

Figure 1.1: IQS7221G Block Diagram

## Contents

| 1 | Device Overview11.1Main Features11.2Applications21.3Block Diagram2                                                                                                                                                                                                                                                                                                                                     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Hardware Connections       7         2.1       QFN20 Pin Diagram       7         2.2       Pin Attributes       7         2.3       Signal Descriptions       8         2.4       Reference Schematic       9         2.4.1       Hall-Rotation Sensing       9         2.4.2       Hall-Rotation with Self-Capacitance and Inductive Sensing       10         2.5       Hall Plate Positions       11 |

| 3 | Electrical Characteristics123.1Absolute Maximum Ratings123.2Recommended Operating Conditions123.3ESD Rating133.4Current Consumption14                                                                                                                                                                                                                                                                  |

| 4 | Timing and Switching Characteristics154.1Reset Levels154.2Miscellaneous Timings154.3Digital I/O Characteristics154.4I²C Characteristics154.5Power-On I²C Timing164.5.1Power-On Communication Timing with No I²C164.5.2Power-On Communication Timing with I²C16                                                                                                                                         |

| 5 | ProxFusion® Hall Sensor Module175.1Magnet Orientation175.2Hall Rotation Measurements175.3Hall Rotation Channels185.4Automatic Tuning Implementation (ATI)185.4.1Runtime ATI185.5Filtering185.6Interval UI195.7High-accuracy Mode195.8Stationary Detection205.9Angle Offset Compensation205.10Automatic Interval Centering205.11Quadrature Output225.12Buffered Intervals22                             |

| 6 | ProxFusion® Channels         23           6.1         Sensing Modes         23           6.2         Counts         23           6.2.1         Counts Linearisation         23           6.3         Button Event Detection         24                                                                                                                                                                 |

| <ul> <li>6.4.2 Movement Flags</li> <li>6.5 Dormancy</li> <li>6.6 Automatic Tuning Implementation</li> <li>6.7 Automatic Re-ATI</li> <li>6.8 Debouncing and Hysteresis</li> <li>6.9 Button GPIO</li> <li>7 Freewheel UI</li> <li>7.1 Effects of Freewheel Parameters</li> <li>7.2 Recommended Parameters</li> </ul> | 26<br>26<br>27<br>27<br>28<br>28<br>29<br>29 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <ul> <li>6.9 Button GPIO</li></ul>                                                                                                                                                                                                                                                                                 | 28<br>29<br>29                               |

| <ul> <li>7.1 Effects of Freewheel Parameters</li></ul>                                                                                                                                                                                                                                                             | 29                                           |

| 7.2 Recommended Parameters                                                                                                                                                                                                                                                                                         |                                              |

| 9 Hantia III                                                                                                                                                                                                                                                                                                       |                                              |

| 8 Haptic UI                                                                                                                                                                                                                                                                                                        | 32                                           |

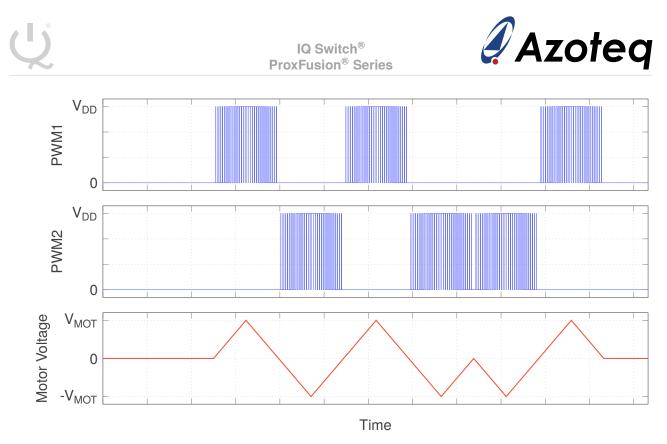

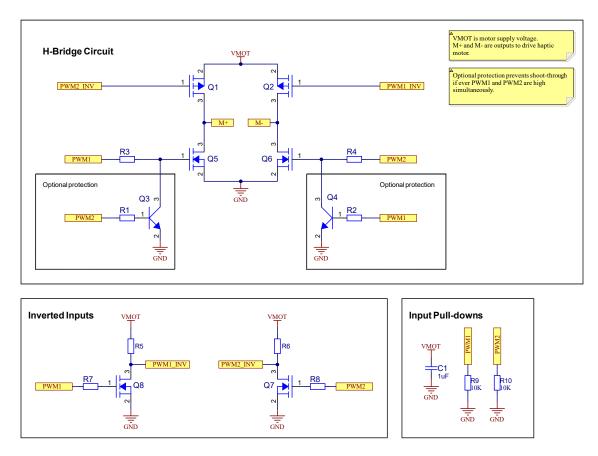

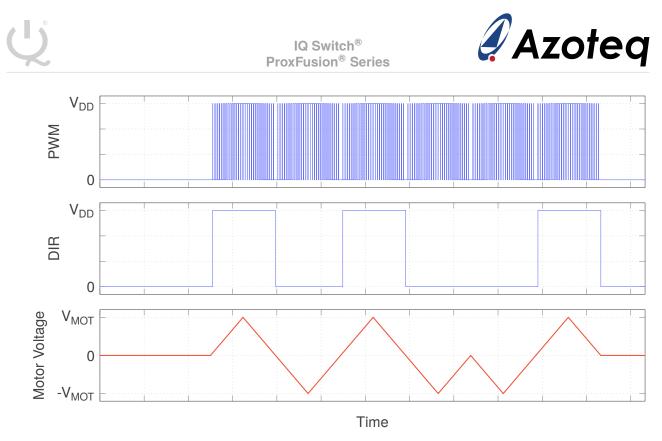

| 8.1       Supported H-Bridge Devices         8.1.1       PWM1/PWM2                                                                                                                                                                                                                                                 |                                              |

| 8.1.2 PWM//PWM2                                                                                                                                                                                                                                                                                                    |                                              |

| 8.2 Enabling Haptics                                                                                                                                                                                                                                                                                               |                                              |

| 8.3 LRA Frequency                                                                                                                                                                                                                                                                                                  |                                              |

| 8.4 Haptic Waveforms                                                                                                                                                                                                                                                                                               |                                              |

| 8.4.1 Amplitude                                                                                                                                                                                                                                                                                                    | 37                                           |

| 8.4.2 Duration                                                                                                                                                                                                                                                                                                     | 37                                           |

| 8.4.3 Direction                                                                                                                                                                                                                                                                                                    | 37                                           |

| 8.5 Haptic Triggers                                                                                                                                                                                                                                                                                                |                                              |

| 8.5.1 Interval UI Triggers                                                                                                                                                                                                                                                                                         |                                              |

| 8.5.2ProxFusion UI Triggers                                                                                                                                                                                                                                                                                        |                                              |

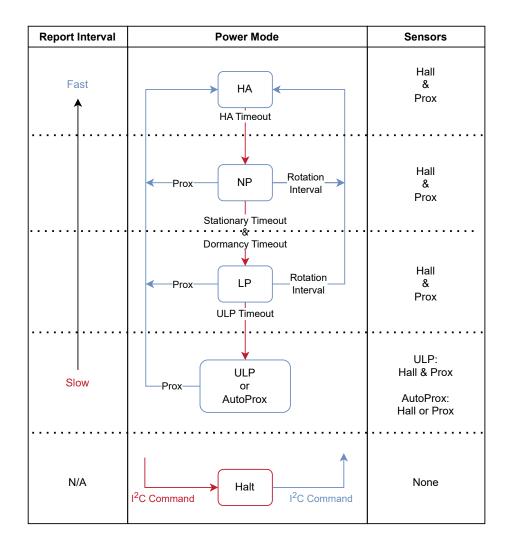

| 9 Power Options                                                                                                                                                                                                                                                                                                    | 40                                           |

| 10 Additional Features                                                                                                                                                                                                                                                                                             | 42                                           |

| 10.1 Debug and Display Software (GUI)                                                                                                                                                                                                                                                                              | 42                                           |

| 10.2 Main Oscillator                                                                                                                                                                                                                                                                                               | 42                                           |

| 10.3 Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                          |                                              |

| 10.4 Reset                                                                                                                                                                                                                                                                                                         |                                              |

| 10.4.1 Reset Indication                                                                                                                                                                                                                                                                                            |                                              |

| 10.4.2 Software Reset                                                                                                                                                                                                                                                                                              | 43                                           |

| 11 I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                      | 44                                           |

| 11.1 I <sup>2</sup> C Module Specification                                                                                                                                                                                                                                                                         | 44                                           |

| 11.2 I <sup>2</sup> C Address                                                                                                                                                                                                                                                                                      |                                              |

| 11.3 I <sup>3</sup> C Compatibility                                                                                                                                                                                                                                                                                |                                              |

| 11.4 I <sup>2</sup> C Starting Behaviour                                                                                                                                                                                                                                                                           |                                              |

| 11.5 Memory Map Data                                                                                                                                                                                                                                                                                               |                                              |

| 11.6 RDY/IRQ                                                                                                                                                                                                                                                                                                       |                                              |

| 11.7 Read and Write Operations                                                                                                                                                                                                                                                                                     |                                              |

| 11.7.1 I <sup>2</sup> C Read From Specific Address                                                                                                                                                                                                                                                                 |                                              |

| 11.7.2I <sup>2</sup> C Write To Specific Address                                                                                                                                                                                                                                                                   |                                              |

|    | 11.9<br>11.10                                 | Terminate Communication       Invalid Communications Return         Event Mode Communication       Invalid Communication         11.11.1       Events              | 46<br>47<br>47<br>47<br>47        |

|----|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 12 | I <sup>2</sup> C M                            | emory Map                                                                                                                                                          | 49                                |

| 13 | 13.1                                          | Ordering Code                                                                                                                                                      | <b>53</b><br>53<br>53<br>53<br>53 |

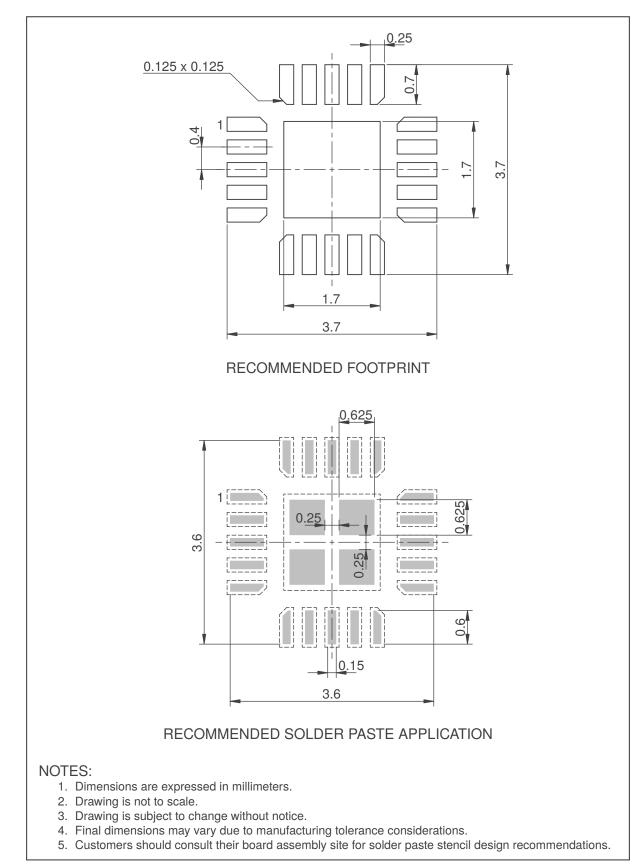

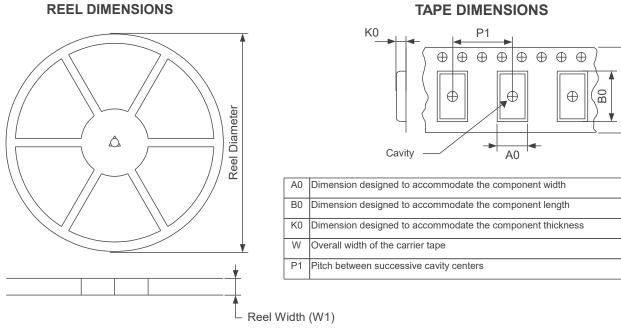

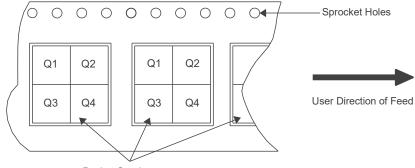

| 14 | Packa<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5 | Package Outline Description – QFN20 (QFR)         Recommended PCB Footprint – QFN20 (QFR)         Tape and Reel Specifications         Moisture Sensitivity Levels | <b>54</b><br>55<br>56<br>57<br>57 |

| Α  |                                               |                                                                                                                                                                    | 58                                |

|    | A.1                                           |                                                                                                                                                                    | 58                                |

|    | A.2                                           | 5 ( )                                                                                                                                                              | 58                                |

|    | A.3                                           |                                                                                                                                                                    | 59                                |

|    | A.4                                           |                                                                                                                                                                    | 59                                |

|    | A.5                                           |                                                                                                                                                                    | 60                                |

|    | A.6                                           |                                                                                                                                                                    | 61                                |

|    | A.7                                           | <b>y b c c y</b>                                                                                                                                                   | 62                                |

|    | A.8                                           |                                                                                                                                                                    | 62                                |

|    | A.9                                           | 5 ( )                                                                                                                                                              | 63                                |

|    | A.10<br>A.11                                  | 5                                                                                                                                                                  | 64<br>64                          |

|    | A.11<br>A.12                                  | <u> </u>                                                                                                                                                           | 64                                |

|    | A.12                                          |                                                                                                                                                                    | 65                                |

|    | A.14                                          |                                                                                                                                                                    | 65                                |

|    | A.15                                          |                                                                                                                                                                    | 65                                |

|    | A.16                                          |                                                                                                                                                                    | 65                                |

|    | A.17                                          |                                                                                                                                                                    | 66                                |

|    | A.18                                          |                                                                                                                                                                    | 66                                |

|    | A.19                                          |                                                                                                                                                                    | 66                                |

|    | A.20                                          |                                                                                                                                                                    | 67                                |

|    | A.21                                          | CH0 Movement Debounce (0xBB)                                                                                                                                       | 67                                |

|    | A.22                                          | CH0 Sensor Settings 1 (0xBC)                                                                                                                                       | 67                                |

|    | A.23                                          | CH0 Sensor Settings 2 (0xBD)                                                                                                                                       | 68                                |

|    | A.24                                          | CH1 Betas 1 (0xC3)                                                                                                                                                 | 69                                |

|    | A.25                                          |                                                                                                                                                                    | 69                                |

|    | A.26                                          |                                                                                                                                                                    | 69                                |

|    | A.27                                          |                                                                                                                                                                    | 70                                |

|    | A.28                                          | 5 ( )                                                                                                                                                              | 70                                |

|    | A.29                                          | CH1 Sensor Settings 2 (0xCD)                                                                                                                                       | 71                                |

| A.30 | Haptic Global Settings (0xD0)      | 71 |

|------|------------------------------------|----|

| A.31 | Button Haptics Triggers (0xD2)     | 71 |

| A.32 | Waveform 1 Stage 1 Settings (0xE1) | 72 |

| A.33 | Waveform 1 Stage 2 Settings (0xE3) | 72 |

| A.34 | Waveform 2 Stage 1 Settings (0xE5) | 73 |

| A.35 | Waveform 2 Stage 2 Settings (0xE7) | 73 |

| A.36 | Waveform 3 Stage 1 Settings (0xE9) | 73 |

| A.37 | Waveform 3 Stage 2 Settings (0xEB) | 73 |

| A.38 | Waveform 4 Stage 1 Settings (0xED) | 74 |

| A.39 | Waveform 4 Stage 2 Settings (0xEF) | 74 |

### 2 Hardware Connections

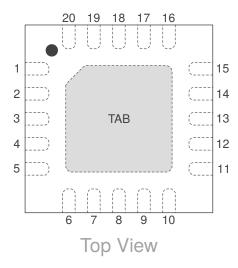

### 2.1 QFN20 Pin Diagram

#### Table 2.1: 20-pin QFN Package (Top View)

| Pin no.   | Signal name Pin no. |       | Signal name |  |

|-----------|---------------------|-------|-------------|--|

| 1         | VDD                 | DD 11 |             |  |

| 2 VREGD   |                     | 12    | Tx7         |  |

| 3         | VSS                 | 13    | NC          |  |

| 4         | VREGA               | 14    | QUAD_A      |  |

| 5         | Rx0/Tx0             | 15    | GPIO3       |  |

| 6         | Rx1/Tx1             | 16    | GPIO4       |  |

| 7         | Rx2/Tx2             | 17    | QUAD_B      |  |

| 8         | Rx3/Tx3             | 18    | SCL         |  |

| 9         | Tx4                 | 19    | SDA         |  |

| 10        | Tx5                 | 20    | RDY         |  |

|           |                     |       |             |  |

| Area name | Signal name         |       |             |  |

| Area name        | Signal name            |

|------------------|------------------------|

| TAB <sup>i</sup> | Thermal pad (floating) |

|                  |                        |

### 2.2 Pin Attributes

#### Table 2.2: Pin Attributes

| Pin no.<br>QFN20 | Signal name | Signal type | Buffer type | Power source |

|------------------|-------------|-------------|-------------|--------------|

| 1                | VDD         | Power       | Power       | N/A          |

| 2                | VREGD       | Power       | Power       | N/A          |

| 3                | VSS         | Power       | Power       | N/A          |

| 4                | VREGA       | Power       | Power       | N/A          |

| 5                | Rx0/Tx0     | Analog      |             | VREGA        |

| 6                | Rx1/Tx1     | Analog      |             | VREGA        |

| 7                | Rx2/Tx2     | Analog      |             | VREGA        |

| 8                | Rx3/Tx3     | Analog      |             | VREGA        |

| 9                | Tx4         | Analog      |             | VREGA        |

| 10               | Tx5         | Analog      |             | VREGA        |

| 11               | Tx6         | Analog      |             | VREGA        |

| 12               | Tx7         | Analog      |             | VREGA        |

| 13               | NC          | Analog      |             | VREGA        |

| 14               | QUAD_A      | Digital     |             | VDD          |

| 19               | SDA         | Digital     |             | VDD          |

| 18               | SCL         | Digital     |             | VDD          |

| 15               | GPIO3       | Digital     |             | VDD          |

| 16               | GPIO4       | Digital     |             | VDD          |

| 17               | QUAD_B      | Digital     |             | VDD          |

| 20               | RDY         | Digital     |             | VDD          |

<sup>i</sup> It is recommended to connect the thermal pad (TAB) to VSS.

## 2.3 Signal Descriptions

| Function                | Signal name | Pin no.<br>QFN20 | Pin type <sup>ii</sup> | Description                                         |

|-------------------------|-------------|------------------|------------------------|-----------------------------------------------------|

|                         | Rx0/Tx0     | 5                | IO                     |                                                     |

|                         | Rx1/Tx1     | 6                | IO                     |                                                     |

|                         | Rx2/Tx2     | 7                | IO                     |                                                     |

|                         | Rx3/Tx3     | 8                | IO                     | ProxFusion <sup>®</sup> channel                     |

| ProxFusion <sup>®</sup> | Tx4         | 9                | 0                      |                                                     |

|                         | Tx5         | 10               | 0                      |                                                     |

|                         | Tx6         | 11               | 0                      |                                                     |

|                         | Tx7         | 12               | 0                      |                                                     |

|                         | NC          | 13               | 0                      | NC pad                                              |

|                         | QUAD_A      | 14               | 0                      | Quadrature pin                                      |

|                         | GPIO3       | 15               | 0                      | Haptics PWM2/DIR pin                                |

| GPIO                    | GPIO4       | 16               | 0                      | Haptic PWM1 or Button output pin                    |

| ano                     | QUAD_B      | 17               | 0                      | Quadrature pin                                      |

|                         | RDY         | 20               | 0                      | RDY pad<br>VPP input for OTP                        |

| l <sup>2</sup> C        | SDA         | 19               | IO                     | I <sup>2</sup> C data                               |

|                         | SCL         | 18               | IO                     | I <sup>2</sup> C clock                              |

|                         | VDD         | 1                | Р                      | Power supply input voltage                          |

|                         | VREGD       | 2                | Р                      | Internal regulated supply output for digital domain |

| Power                   | VSS         | 3                | Р                      | Analog/digital ground                               |

|                         | VREGA       | 4                | Р                      | Internal regulated supply output for analog domain  |

#### Table 2.3: Signal Descriptions

<sup>ii</sup> Pin Types: I = Input, O = Output, IO = Input or Output, P = Power.

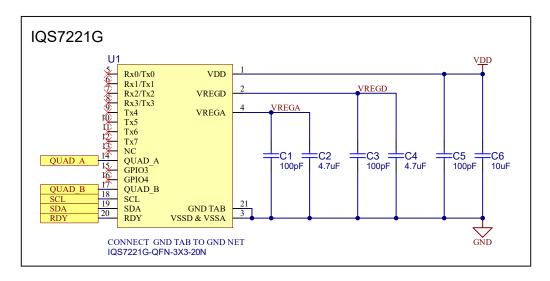

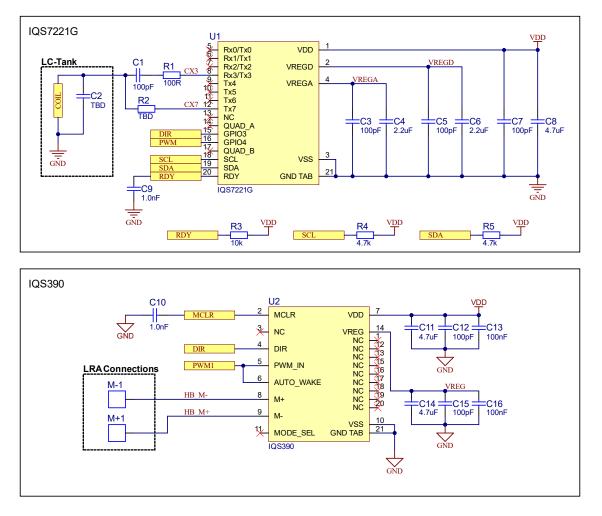

### 2.4 Reference Schematic

### 2.4.1 Hall-Rotation Sensing

Minimal example schematic for Hall-rotation sensing and quadrature output.

Figure 2.1: IQS7221G Reference Schematic

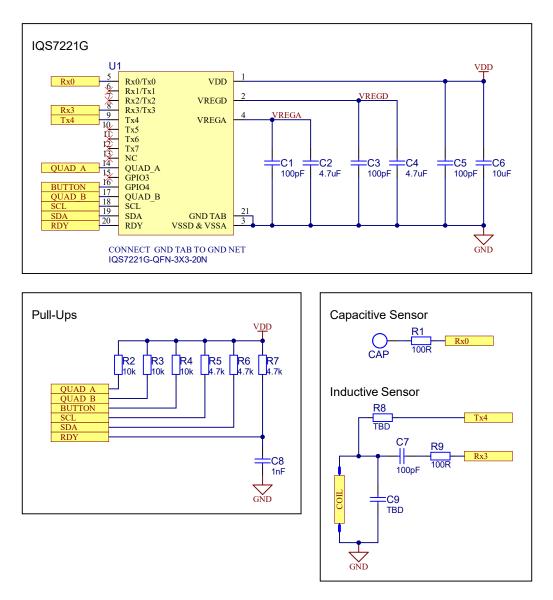

### 2.4.2 Hall-Rotation with Self-Capacitance and Inductive Sensing

Example schematic for an application with Hall-rotation sensing, inductive button, and a capacitive wake-up channel. Quadrature pins provide rotation information, and GPIO4 provides the state of the inductive button (open-drain active low).

Figure 2.2: IQS7221G Reference Schematic with Self-Capacitive and Inductive Sensing

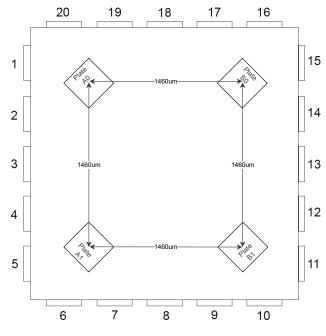

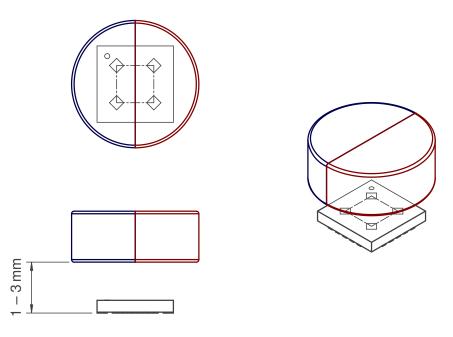

### 2.5 Hall Plate Positions

Figure 2.3: Plate Layout QFN (Top View)

## **3** Electrical Characteristics

## 3.1 Absolute Maximum Ratings

#### Table 3.1: Absolute Maximum Ratings

|                                                                        | Min  | Max                      | Unit |

|------------------------------------------------------------------------|------|--------------------------|------|

| Voltage applied at VDD pin to VSS                                      | 1.8  | 3.6                      | V    |

| Voltage applied to any ProxFusion <sup>®</sup> pin (referenced to VSS) | -0.3 | VREGA                    | V    |

| Voltage applied to any other pin (referenced to VSS)                   | -0.3 | VDD + 0.3<br>(3.6 V max) | V    |

| Storage temperature, T <sub>stg</sub>                                  | -40  | 85                       | °C   |

## 3.2 Recommended Operating Conditions

#### Table 3.2: Recommended Operating Conditions

|                                             |                                                                                                                                                                                                         | Min                  | Nom                  | Max                                   | Unit |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|---------------------------------------|------|

|                                             | Supply voltage applied at VDD pin:                                                                                                                                                                      |                      |                      |                                       |      |

| VDD                                         | F <sub>OSC</sub> = 14 MHz                                                                                                                                                                               | 1.8                  |                      | 3.6                                   | V    |

|                                             | F <sub>OSC</sub> = 18 MHz                                                                                                                                                                               | 2.2                  |                      | 3.6                                   |      |

|                                             | Internal regulated supply output for analog domain:                                                                                                                                                     |                      |                      |                                       |      |

| VREGA                                       | F <sub>OSC</sub> = 14 MHz                                                                                                                                                                               | 1.49                 | 1.53                 | 1.57                                  | V    |

|                                             | F <sub>OSC</sub> = 18 MHz                                                                                                                                                                               | 1.7                  | 1.75                 | 1.79                                  |      |

|                                             | Internal regulated supply output for digital domain:                                                                                                                                                    |                      |                      |                                       |      |

| VREGD                                       | $F_{OSC} = 14 \text{ MHz}$                                                                                                                                                                              | 1.56                 | 1.59                 | 1.64                                  | V    |

|                                             | F <sub>OSC</sub> = 18 MHz                                                                                                                                                                               | 1.75                 | 1.8                  | 1.85                                  |      |

| VSS                                         | Supply voltage applied at VSS pin                                                                                                                                                                       |                      | 0                    |                                       | V    |

| T <sub>A</sub>                              | Operating free-air temperature                                                                                                                                                                          | -40                  | 25                   | 85                                    | °C   |

| C <sub>VDD</sub>                            | Recommended capacitor at VDD                                                                                                                                                                            | 2×C <sub>VREGA</sub> | 3×C <sub>VREGA</sub> |                                       | μF   |

| C <sub>VREGA</sub>                          | Recommended external buffer capacitor at VREGA, ESR $\leq$ 200 m $\Omega$                                                                                                                               | 2 <sup>i</sup>       | 4.7                  | 10                                    | μF   |

| C <sub>VREGD</sub>                          | Recommended external buffer capacitor at VREGD, ESR $\leq$ 200 m $\Omega$                                                                                                                               | 2 <sup>i</sup>       | 4.7                  | 10                                    | μF   |

| Cx <sub>SELF-VSS</sub>                      | Maximum capacitance between ground and all external electrodes on all ProxFusion <sup>®</sup> blocks (self-capacitance mode)                                                                            | 1                    |                      | 400 <sup>ii</sup>                     | pF   |

| Cm <sub>Tx-Rx</sub>                         | Capacitance between receiving and transmitting electrodes on all ProxFusion <sup>®</sup> blocks (mutual-capacitance mode)                                                                               | 0.2                  |                      | 9 <sup>ii</sup>                       | pF   |

| Cp <sub>Rx-VSS</sub>                        | Maximum capacitance between ground and all<br>external electrodes on all ProxFusion® blocks<br>Mutual-capacitance mode, F <sub>xfer</sub> = 1 MHz<br>Mutual-capacitance mode, F <sub>xfer</sub> = 4 MHz |                      |                      | 100 <sup>ii</sup><br>25 <sup>ii</sup> | pF   |

| Cp <sub>Rx-VSS</sub><br>Cm <sub>Tx-Rx</sub> | Capacitance ratio for optimal SNR in mutual-capacitance mode <sup>iii</sup>                                                                                                                             | 10                   |                      | 20                                    | n/a  |

| RCx <sub>Rx/Tx</sub>                        | Series (in-line) resistance of all mutual-capacitance pins (Tx & Rx pins) in mutual-capacitance mode                                                                                                    | Oiv                  | 0.47                 | 10 <sup>v</sup>                       | kΩ   |

| RCx <sub>SELF</sub>                         | Series (in-line) resistance of all self-capacitance pins in self-capacitance mode                                                                                                                       | Oiv                  | 0.47                 | 10 <sup>v</sup>                       | kΩ   |

### 3.3 ESD Rating

#### Table 3.3: ESD Rating

|                                     |                                                                  | Value | Unit |

|-------------------------------------|------------------------------------------------------------------|-------|------|

| $V_{(ESD)}$ Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>vi</sup> | ±4000 | V    |

<sup>&</sup>lt;sup>1</sup> Absolute minimum allowed capacitance value is 1 μF, after taking derating, temperature, and worst-case tolerance into account. Please refer to AZD004 for more information regarding capacitor derating.

ii RCx =  $0 \Omega$ .

<sup>&</sup>lt;sup>iii</sup> Please note that the maximum values for Cp and Cm are subject to this ratio.

<sup>&</sup>lt;sup>iv</sup> Nominal series resistance of 470 Ω is recommended to prevent received and emitted EMI effects. Typical resistance also adds additional ESD protection.

<sup>&</sup>lt;sup>v</sup> Series resistance limit is a function of  $F_{xfer}$  and the circuit time constant, *RC*.  $R_{max} \times C_{max} = \frac{1}{(6 \times F_{xfer})}$  where *C* is the pin capacitance to VSS.

<sup>&</sup>lt;sup>vi</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±4000 V may actually have higher performance.

### 3.4 Current Consumption

The current consumption of the IQS7221G is highly dependent on the specific parameters configured during initialisation, as well as on the frequency and duration of I<sup>2</sup>C communications. Therefore, the following tables serve as an illustration of the expected power consumption for similar configurations<sup>vii</sup>. All measurements are taken with *Event Mode* enabled, without any sensor activations, without any I<sup>2</sup>C communications, and with quadrature disabled. As a result, current consumption values shown here may be slightly lower than in practical applications.

All other settings, unless stated otherwise, are kept default.

Current consumption values are provided for both 14 MHz and 18 MHz  $F_{OSC}$  configurations. For more information, please refer to Section 10.2.

|               |                  | Current Consumption [µA] |                     |      |          |           |

|---------------|------------------|--------------------------|---------------------|------|----------|-----------|

| Power Mode    | Report Rate [ms] | Hall &<br>Self-Cap       | Hall &<br>Inductive | Hall | Self-Cap | Inductive |

| High-Accuracy | 5                | 460                      | 620                 | 350  | 230      | 360       |

| Normal        | 40               | 75                       | 98                  | 60   | 36       | 55        |

| Low           | 200              | 18                       | 22                  | 15   | 10       | 13        |

| Ultra-Low     | 500              | 6.7                      | 8.5                 | 5.5  | 3.5      | 4.9       |

| Halt          | 3000             |                          |                     | 1.3  | ·        |           |

#### Table 3.4: IQS7221G Typical Current Consumption at 14 MHz F<sub>OSC</sub>

#### Table 3.5: IQS7221G Typical Current Consumption at 18 MHz $F_{OSC}$

|               |                  | Current Consumption [µA] |                     |      |          |           |

|---------------|------------------|--------------------------|---------------------|------|----------|-----------|

| Power Mode    | Report Rate [ms] | Hall &<br>Self-Cap       | Hall &<br>Inductive | Hall | Self-Cap | Inductive |

| High-Accuracy | 5                | 530                      | 650                 | 387  | 233      | 315       |

| Normal        | 40               | 80                       | 97                  | 63   | 40       | 53        |

| Low           | 200              | 19                       | 22                  | 16   | 11       | 13        |

| Ultra-Low     | 500              | 7.3                      | 8.6                 | 5.9  | 4.0      | 5.0       |

| Halt          | 3000             |                          | 1                   | 1.3  | 1        |           |

vii These measurements are based on bench testing and have not been characterised over large volumes.

### 4 Timing and Switching Characteristics

#### 4.1 Reset Levels

#### Table 4.1: Reset Levels

| Paramete         | r                                             | Min | Max    | Unit |

|------------------|-----------------------------------------------|-----|--------|------|

| V                | Power-up (Reset trigger) – slope > 100 V/s    |     | 1.65 V |      |

| V <sub>VDD</sub> | Power-down (Reset trigger) – slope < -100 V/s | 0.9 |        | v    |

### 4.2 Miscellaneous Timings

#### Table 4.2: Miscellaneous Timings

| Parameter         |                                                     | Min   | Тур        | Max   | Unit |

|-------------------|-----------------------------------------------------|-------|------------|-------|------|

| Fosc              | Master CLK frequency tolerance 14 MHz               | 13.23 | 14         | 14.77 | MHz  |

| Fosc              | Master CLK frequency tolerance 18 MHz               | 17.1  | 18         | 19.54 | MHz  |

| F <sub>xfer</sub> | Charge transfer frequency (derived from $F_{OSC}$ ) | 42    | 500 - 1500 | 4500  | kHz  |

## 4.3 Digital I/O Characteristics

#### Table 4.3: Digital I/O Characteristics

| Parameter          |                                      | <b>Test Conditions</b>      | Min       | Max       | Unit |

|--------------------|--------------------------------------|-----------------------------|-----------|-----------|------|

| V <sub>OL</sub>    | SDA & SCL Output low voltage         | I <sub>sink</sub> = 20 mA   |           | 0.3       | V    |

| V <sub>OL</sub>    | GPIO <sup>i</sup> Output low voltage | I <sub>sink</sub> = 10 mA   |           | 0.15      | V    |

| V <sub>OH</sub>    | Output high voltage                  | I <sub>source</sub> = 20 mA | VDD - 0.2 |           | V    |

| V <sub>IL</sub>    | Input low voltage                    |                             |           | VDD × 0.3 | V    |

| V <sub>IH</sub>    | Input high voltage                   |                             | VDD × 0.7 |           | V    |

| C <sub>b_max</sub> | SDA & SCL maximum bus<br>capacitance |                             |           | 550       | pF   |

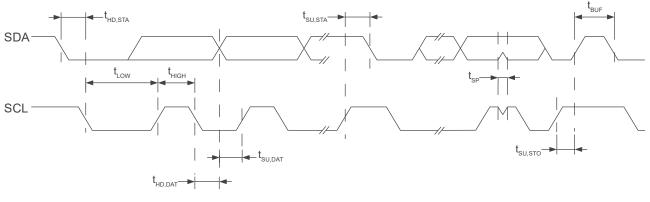

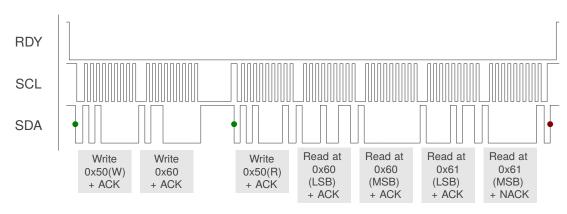

## 4.4 I<sup>2</sup>C Characteristics

#### Table 4.4: I<sup>2</sup>C Characteristics

| Parameter           |                                                     | Min  | Max  | Unit |

|---------------------|-----------------------------------------------------|------|------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                 |      | 1000 | kHz  |

| t <sub>HD,STA</sub> | Hold time (repeated) START                          | 0.26 |      | μs   |

| t <sub>SU,STA</sub> | Setup time for a repeated START                     | 0.26 |      | μs   |

| t <sub>HD,DAT</sub> | Data hold time                                      | 0    |      | ns   |

| t <sub>SU,DAT</sub> | Data setup time                                     | 50   |      | ns   |

| t <sub>SU,STO</sub> | Setup time for STOP                                 | 0.26 |      | μs   |

| t <sub>SP</sub>     | Pulse duration of spikes suppressed by input filter | 0    | 50   | ns   |

<sup>i</sup> Refers to QUAD\_A, GPIO3, GPIO4, and QUAD\_B pins.

Figure 4.1: I<sup>2</sup>C Mode Timing Diagram

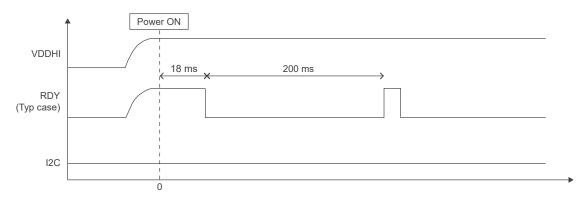

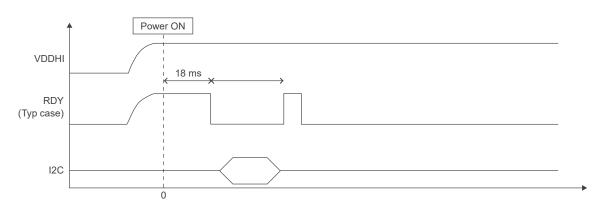

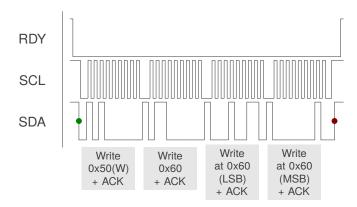

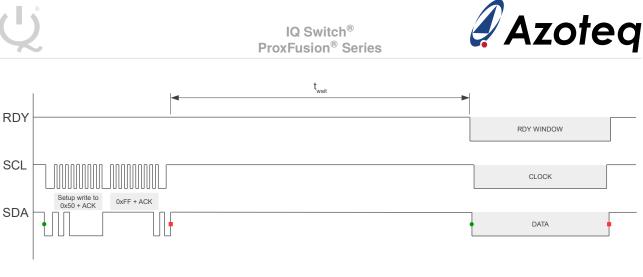

## 4.5 Power-On I<sup>2</sup>C Timing

#### 4.5.1 Power-On Communication Timing with No I<sup>2</sup>C

### 4.5.2 Power-On Communication Timing with I<sup>2</sup>C

### 5 ProxFusion<sup>®</sup> Hall Sensor Module

The IQS7221G contains four equally-spaced Hall plates that measure the magnetic field strength and orientation of a nearby diametrically-polarised magnet. These Hall plates are used to calculate the relative angle of a magnet with regards to the IC, in an on-axis orientation. The angle can be divided into discrete intervals using the Interval UI, providing a convenient interface for scroll wheel applications.

Two ProxFusion<sup>®</sup> modules allow for simultaneous sampling of two Hall plates at a time, improving the responsiveness of the system. The Hall sensor provides an interval UI to track the current angle of the magnet. The I<sup>2</sup>C interface can be used to track the absolute angle of the magnet. The quadrature outputs provide an interface for relative angle tracking in low-power systems and can act as a drop-in replacement for existing digital rotational encoders.

#### 5.1 Magnet Orientation

The IQS7221G is designed to be used in an on-axis orientation with regard to the magnet, as shown in Figure 5.1.

Figure 5.1: Magnet Orientation of an On-axis Angle Measurement Application

Please refer to AZD127 for more information regarding on-axis design guidelines.

### 5.2 Hall Rotation Measurements

The IQS7221G provides the angle measurement as three different values:

- > Absolute Angle: Raw angle measurement, provided as an unsigned 16-bit value, where the range [0, 65536) maps to [0°, 360°). This represents the angle of the magnet relative to the IC.

- > Processed Angle: Angle measurement after post-processing, also an unsigned 16-bit value. This output is filtered and includes an angular offset. This output can be used for applications requiring high-resolution measurements.

> *Interval*: The output of the interval UI, which divides the unsigned 16-bit processed angle into several sections, or intervals. This output is recommended for applications with mechanical ratchets and is supplemented by the hysteresis, auto-zero, and quadrature features.

### 5.3 Hall Rotation Channels

The Hall-effect rotation measurement on the IQS7221G relies on two measurements on each of the four Hall plates, where the second measurement is inverted to the first. These two measurements allow for the calculation of a reference value and a differential value, from which the relative strength of the magnetic field can be inferred. The reference value is calculated as the average of the two measurements, and the differential value is calculated as the difference between the measurements.

As a result, the IQS7221G performs eight Hall-effect measurements, four of which are inverted to the others. These measurement values (channels) are available in the *Hall Plate Counts* and *Hall Reference* registers.

#### 5.4 Automatic Tuning Implementation (ATI)

ATI is an automatic sensor calibration algorithm that configures the *Hall Plate Offsets* to ensure accurate Hall-effect sensing for a range of different magnet sizes and strengths. The ATI aims to modify the Hall plate settings such that the Hall channel reference values are within the range defined by the *Target* and *ATI Band* parameters. Recommended value for the target is between 8000 and 14000.

The *Hall Gain* value is a constant parameter that must be chosen at design time. This can be done with the aid of the IQS7221G GUI. Typically, the Hall Gain value can be chosen such that the Hall channels swing around  $\pm 2000$  to  $\pm 4000$  counts from the reference over a full rotation of the magnet. Once this Gain value is chosen, it can be fixed for all modules across production. The ATI feature will then compensate for any variation across production.

#### 5.4.1 Runtime ATI

ATI is performed automatically at start-up, as well as when all the following criteria are met:

- > The Stationary flag is set; see Section 5.8.

- > The *Hall Reference* of a channel is outside the threshold defined by Equation (1).

|Hall Target – Hall Reference| > Hall ATI Band

> Runtime ATI is enabled in *Hall UI Settings*.

### 5.5 Filtering

The IQS7221G includes a dynamic angle filter that increases its bandwidth based on the magnet's current speed. This allows the filter to remove most of the high-frequency noise while the magnet is stationary, and prevents the filter from aliasing during high-speed rotations. The overall strength of the filter can be adjusted with the *Angle Filter Beta* value in the *Hall Angle Betas* register.

In Low and Ultra Low power modes, the *Low Power Beta* is used instead. This should be set to a *larger* value than the normal beta value, to reduce measured jitter at lower report rates.

(1)

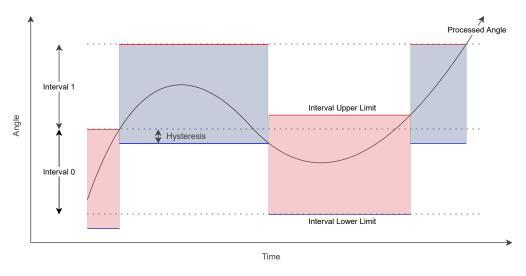

## 5.6 Interval UI

The interval UI divides the 16-bit processed angle into a value between 0 and the *Number of Intervals*, where the size of each interval is defined as:

Interval Size =  $\frac{2^{16}}{\text{Number of Intervals}}$ . (2)

This is especially useful for applications that do not require a high measurement resolution, or that use mechanical ratchets.

The interval UI is also used for the quadrature UI. On interval change, the IQS7221G will output a quadrature event on the quadrature pins. The device can also open an  $I^2C$  communications window on interval change if  $I^2C$  is enabled and *Hall Events* are enabled.

### 5.6.1 Interval Hysteresis

The Interval Hysteresis prevents the interval output from jittering between two intervals, causing unnecessary interval change events. The behaviour of the hysteresis is shown in Figure 5.2.

Figure 5.2: Illustration of the Interval Size and Interval Hysteresis

The amount of hysteresis applied can be modified by changing the *Interval Hysteresis* value. Hysteresis is a 16-bit value, in the same unit as the Processed Angle. Hysteresis should therefore be chosen based on the interval size calculated in the previous section, and on the amplitude of the noise on the Processed Angle.

## 5.7 High-accuracy Mode

The High-Accuracy mode of the IQS7221G will increase the report rate of the device to sample Hall rotation measurements more accurately and to reduce aliasing during high rotation rates.

The IQS7221G will enter High-Accuracy mode in the event of:

- > An interval change,

- > Freewheeling, if the "Force High-Accuracy" bit is set under the Hall UI Settings register.

The *High-Accuracy* flag will remain set for the duration of the *High-Accuracy Timeout*. This flag is used to identify whether to transition into the High-Accuracy power mode, and can be configured to signal an automatic interval centering event when High-Accuracy mode is exited.

### 5.8 Stationary Detection

The IQS7221G will set a *Stationary* flag if no movement is detected during the period defined by the *Stationary Timeout* value. This Stationary flag is used to identify whether to go into a lower power mode. Runtime ATI for the Hall channels is also only executed when the Stationary flag is set.

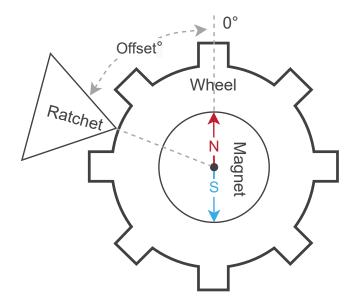

### 5.9 Angle Offset Compensation

Angle offset compensation is applied to ensure the output angle corresponds to the angle of the wheel, rather than the raw angle of the magnet, as shown in Figure 5.3. This is especially important for ratchet applications, where the intervals generated by the IC must match the mechanically-defined intervals of the wheel.

Figure 5.3: Illustration of the Absolute Angle Offset

The angle offset is updated when the *Zero* command in the *System Settings 2* register is set. This sets the Processed Angle to the centre of interval 0, and thus adjusts the angle offset accordingly. The *Zero* command is also set automatically on start-up.

The angle offset is also modified by the automatic interval centering functionality, to align the intervals with a mechanical ratchet automatically.

Finally, the angle offset can be manually changed via the Angle Offset register.

## 5.10 Automatic Interval Centering

The interval centering functionality (or "auto-zero") of the IQS7221G allows the device to modify the absolute angle offset of the Processed Angle such that the Processed Angle is at the centre of the current interval. This dynamically adjusts the absolute angle offset until the Processed Angle aligns with the physical intervals of a ratchet device.

The auto-zero functionality can be set to one of four different modes in the Hall UI Settings:

- > Off: The device will never allow an automatic interval zero action to happen, and the master device will have to send an instruction over I<sup>2</sup>C to set the Zero bit.

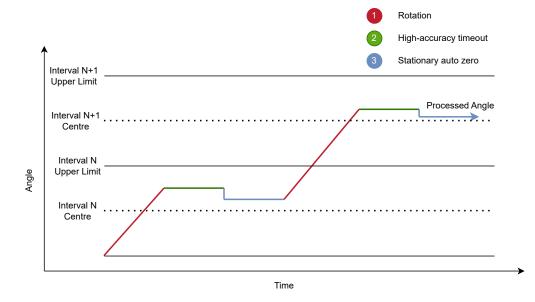

- Stationary: An auto-zero event will occur when the High-Accuracy timeout event occurs. A single adjustment is made to the absolute angle offset each time the device exits High-Accuracy mode. The *Auto-Zero Beta* parameter defines the size of the adjustment, with an auto-zero beta value of 0 resulting in a jump to the exact center of the interval. This behaviour can be seen in Figure 5.4.

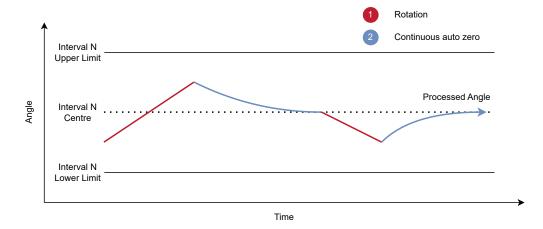

- > Continuous: The auto-zero filter will cause the Processed Angle to move continuously towards the centre of the current interval. It is recommended to use an auto-zero beta value of 10 or higher to allow the Processed Angle to move between intervals during slower rotations. This mode is recommended for devices without a mechanical ratchet. This behaviour can be viewed in Figure 5.5.

- > Release: An auto-zero event will occur on a Movement Exit event on ProxFusion Channel 0. If Channel 0 is configured as a capacitive touch channel, this exit event could indicate that the user released the device.

Figure 5.4: Stationary Auto-zero Behaviour

### 5.11 Quadrature Output

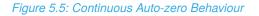

The quadrature output provides feedback over two GPIOs (QUAD\_A and QUAD\_B) when the value of the current interval changes. This functionality can be used for standalone applications where the master device would not need to poll the current interval value over I<sup>2</sup>C but would rather monitor the state of the two quadrature outputs. A visual example of the quadrature output is displayed in Figure 5.6.

A single interval change is represented by a rising or falling edge on both quadrature pins. The direction of the interval change is defined by which pin changes state first. For a positive rotation, the state of QUAD\_A changes first, and for a negative rotation, the state of QUAD\_B changes first. The period between the change in states of each quadrature output is defined by the *Quadrature Flank Delay* parameter. The quadrature flank delay parameter will also define the maximum report rate of the quadrature output.

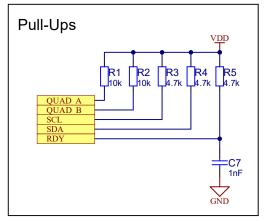

The quadrature output pins can be configured as either push-pull or open-drain by setting the *Quadrature Mode* parameter. If open-drain mode is used, pull-up resistors must be added to the quadrature lines as shown in the reference schematic in Section 2.4.1.

**Note**: The quadrature output can be fed directly into a standard quadrature decoder. Please note that, since some quadrature decoders expect only one GPIO edge per interval (instead of two), they will record twice the number of intervals.

Figure 5.6: Quadrature IO Timing with Respect to Current Interval

Note the rapid change from interval 2 to 4 in Figure 5.6 resulting in a delayed output of the corresponding flanks, so as not to overwhelm the receiving IC.

## 5.12 Buffered Intervals

During fast rotation, the rate at which intervals are processed may exceed the rate at which quadrature pulses are clocked out. These intervals are buffered in the missed intervals register, and are processed by the quadrature output peripheral at a later time. The buffered intervals can automatically be discarded when the device becomes stationary by setting the *Discard Intervals* bit in the *Hall UI Settings* register.

### 6 ProxFusion<sup>®</sup> Channels

The IQS7221G features two ProxFusion<sup>®</sup> sensing channels that use Azoteq's patented on-chip ProxFusion<sup>®</sup> modules to measure and process relative changes in capacitive and inductive sensors.

Each channel provides two primary Event types – *Button* and *Movement* events. The Button event attempts to track slow changes and long term activations, whereas the Movement event detects smaller, fast changes. Each of these events store their own reference and delta values.

The Movement event on Channel 0 integrates with the Hall-Rotation UI, providing activation triggers for starting and stopping freewheeling.

#### 6.1 Sensing Modes

Each ProxFusion<sup>®</sup> channel independently supports the following sensing modes:

- > Self-capacitive sensing

- > Mutual-capacitive sensing

- > Resonated inductive sensing

The sensing mode of each channel can be modified with the CH0 and CH1 *Sensor Settings 1* registers.

Please refer to the following application notes for more information:

- > AZD004: Overview of Azoteq's ProxFusion® Sensing

- > AZD115: Design Guidelines for Inductive Sensing

- > AZD125: Design Guidelines for Capacitive Touch Sensing

- > AZD144: Inductive Freewheel and Haptics Design Guide (available upon request)

#### 6.2 Counts

Each ProxFusion<sup>®</sup> module reports a capacitance or inductance measurement as a relative, unit-less value referred to as "Raw Counts". These raw counts are related to the number of charge transfer cycles necessary to charge an internal sampling capacitor, and are typically inversely proportional to the signal measured on the external sensor.

#### 6.2.1 Counts Linearisation

The IQS7221G does not directly use the "Raw Counts" obtained from the sensing module, but uses "Linearised Counts", which is calculated as

$$\text{Linearised Counts} = \frac{3276750}{\text{Raw Counts}}.$$

(3)

All references to "Counts" in this datasheet, and in the I<sup>2</sup>C memory map, use these Linearised Counts values.

After linearisation, counts are filtered using a low-pass IIR filter to reduce the high-frequency noise in the measurement. The response of the filter can be adjusted with the *Counts Filter Beta* value in the *CH0 Betas 1* and *CH1 Betas 1* registers. Higher beta values result in a slower filter response, with less noise on the channel.

### 6.3 Button Event Detection

The Button Event attempts to emulate the behaviour of a typical button, which stays in activation for as long as it is pressed.

#### 6.3.1 Long-Term Average

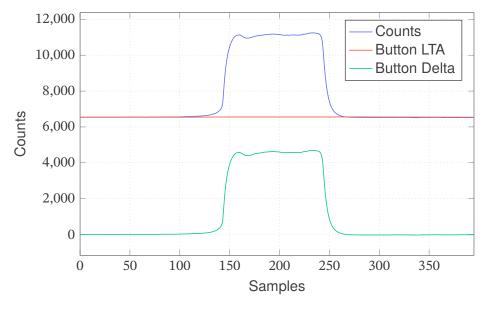

Button events are detected by comparing the filtered counts value to a reference value, known as the Long-Term Average (LTA). While the channel is not in activation, the LTA is slowly updated to track changes in the environment using a low-pass filter.

The difference between the filtered counts and the LTA is stored as the *Delta* value.

$$Delta = LTA - Counts$$

(4)

The delta is used to detect user interaction by comparing it to the *Button Threshold*. The channel enters the active state when the delta exceeds the threshold, and the *Button Active* bit in the *Channel Events* register will be set.

Figure 6.1: Button UI Activation

The LTA is then halted (kept constant) while the Button event is active, or while the delta exceeds the *LTA Halt Threshold*, as shown in Figure 6.1. The LTA Halt Threshold can typically be made smaller than the Button Threshold. This may help increase the sensitivity of the event detection during slower activations, preventing the LTA from drifting during user interaction.

The response of the LTA filter is controlled by the LTA beta values stored in the Channel *Betas 1* and *Betas 2* registers. The *LTA Beta* value sets the response of the filter during High-Accuracy and Normal power modes, whereas the *Low Power LTA Beta* is used during Low and Ultra-Low power modes. The Low Power Beta value should be set to a *larger* value than the Normal Beta value, to maintain adequate sensitivity at lower sampling rates.

#### 6.3.2 Direction

Negative delta values are typically ignored, as they typically indicate an unexpected decrease in signal. If a negative delta value exceeds the *Fast LTA Bound* threshold, the LTA will be updated using the *Fast LTA Beta* filter. This behaviour can be disabled by setting the *Bi-Directional* bit, or the sign of the delta can be inverted by setting the *Inverse* bit in the *Sensor Settings 1* register.

#### 6.3.3 LTA Reseeding

The reseed function of the device will replace the filtered counts and the long-term average value of the channel with the latest sampled counts value to reset the environmental reference of the channel. This may be necessary in certain instances when the Button event gets incorrectly stuck in an activation. Detection of stuck states is controlled by the *Button Timeout* parameter. If the Button event remains active for this timeout duration, the LTA is reseeded automatically. This behaviour can be disabled by setting the timeout parameter to 0.

A Reseed command can also be given manually by setting the corresponding bit in System Settings 2.

#### 6.4 Movement Event Detection

The Movement Event detects small, rapid changes or movements on the ProxFusion channels. This may be used to trigger freewheeling in Hall-rotation applications, or as a simple wake-up event, triggered as the user approaches the sensor.

#### 6.4.1 Long-Term Average

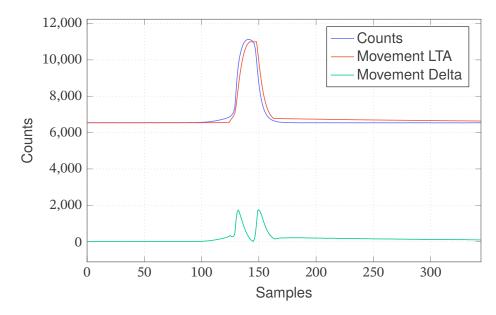

The movement event tracks its own LTA and delta values, separately from the Button event. In contrast to the Button event, the Movement event does not halt its LTA. Instead, it filters using the regular LTA Beta value while not in activation, and filters with the Fast LTA Beta while the event is active (while the delta is larger than the *Movement Threshold*).

The purpose of this is to track increases in the rate of change of counts. This typically occurs as a user is approaching or releasing a proximity sensor. Outside of activations, the LTA is updated slowly to maximise sensitivity to changes in counts. As soon as the delta exceeds the threshold, the fast LTA is used to exit the movement event as quickly as possible, to be ready to detect the next change in counts. This allows for detection of quick flicks typically performed when attempting to activate freewheeling on scroll wheels. An example of the Movement's response to a flick is shown in Figure 6.2.

Figure 6.2: Movement UI Activation

#### 6.4.2 Movement Flags

The primary outputs of the Movement Event are the *Movement Entered* and *Movement Exited* flags in the *Channel Events* registers. The Movement Entered flag is set while the delta exceeds the threshold with a positive sign, and indicates that a user approached the sensor, or entered touch. The Movement Exited flag is set while the delta exceeds the threshold with a negative sign, indicating that the user released the sensor. These flags can be flipped by setting the *Inverse* bit.

Note that the Movement event is not affected by the *Bi-Directional* setting.

During slower movements, the same flag may be set multiple times consecutively. For example, an Enter event may occur repeatedly as the user approaches the sensor.

### 6.5 Dormancy

The touch dormancy flag will be set if the dormancy timeout event occurs after no touch input is received for the period defined in the *Dormancy Timeout* parameter. The IQS7221G is only allowed to enter lower power states once the dormancy flag is set for both channels.

Note that the dormancy timer also acts as a timeout for the LTA Halt flag, if the channel's delta exceeds the LTA Halt Threshold while not in any active state. When dormancy is set, the LTA is reserved, and will then continue to track environmental changes normally.

### 6.6 Automatic Tuning Implementation

The ATI is a sophisticated technology implemented in ProxFusion<sup>®</sup> devices to allow optimal performance of the devices for a wide range of sensing electrode designs, without modification to external components.

The ATI functions by using the *Base* and *Target* parameters to calculate appropriate *Multiplier* and *Compensation* values to achieve an LTA approximately equal to the ATI target value. Note that the base and target values are specified in terms of Linearised Counts, and the base value should always be larger than the target. Typically, a base value of 10000 to 30000 can be used, while a target value between 3500 and 10000 is recommended.

The Coarse Gain parameter in the *ProxFusion Multipliers* registers can be tuned in the GUI. The ATI will then adjust the Fine Multiplier parameter until the counts reach the base value. The Coarse Gain should be manually adjusted at design time until the Fine Divider reaches a value between '4' and '26' after ATI. It can then be fixed across production.

If the ATI algorithm cannot achieve a counts value within the ATI Band, the IQS7221G will set the channel's ATI Error flag.

## 6.7 Automatic Re-ATI

One of the most important features of the automatic Re-ATI functionality of the IQS7221G is that it allows easy and fast recovery from an incorrect ATI, such as when performing ATI during user interaction with the sensor. It is always recommended to have the automatic Re-ATI functionality enabled. When a Re-ATI is performed on the IQS7221G, the *ATI Event* status bit in the *System Flags* register will be momentarily set to indicate that this has occurred.

An automatic Re-ATI operation is performed when the reference of a channel drifts outside the acceptable range around the ATI Target, which is defined by the *ATI Band* parameter. Automatic Re-ATI is also triggered on ATI Error states.

## 6.8 Debouncing and Hysteresis

Each of the Button and Movement events provides two mechanisms to prevent jitter: debouncing and hysteresis.

Debouncing occurs when the Button or Movement delta initially crosses the threshold. It forces the IQS7221G to perform a number of quick measurements (at High-Accuracy report rate), checking that all measurements exceed the threshold. The event's *Debouncing* flag is set as long as debouncing is active. Once debouncing is complete, the event's *Active* flag is set.

The number of high-frequency measurements to execute can be configured independently for entering or exiting the event's active state in the *Debounce* register. Setting the debounce values to '0' or '1' will disable debouncing.

Hysteresis allows the channel to use different enter and exit thresholds for an event. Once the event has entered the active state by exceeding the normal threshold value, the exit threshold is calculated as

Exit Threshold = Threshold

$$\times \left(1 - \frac{\text{Hysteresis Value}}{256}\right)$$

(5)

For example, with a Button threshold of 100 counts, and a hysteresis value of 50, the Button event will enter the Active state when the delta exceeds 100 counts, and will exit the Active state when the delta drops down to  $100 \times (1 - 50/256) = 80$  counts.

A larger hysteresis value is recommended for the Movement Event, as this allows the delta value to return to 0 more quickly after a movement activation.

## 6.9 Button GPIO

GPIO4 may be configured to echo the state of the Button Event of either Channel 0 or 1. GPIO4 provides an open-drain active-low signal. As long as the Button Event is active (delta is above the threshold), GPIO4 is pulled low, until the Prox sensor is released or the Button timeout is reached. A pull-up resistor between GPIO4 and VDD is required.

The Button output may be assigned to either Channel 0 or Channel 1 with the *GPIO Button Channel* setting in the *System Settings 1* register. Note that the Button GPIO output is not compatible with the Haptic UI, as the same pin is required for both features.

## 7 Freewheel UI

The freewheeling UI of the IQS7221G allows the device to continue emulating rotational input when no physical rotation is detected by the Hall-effect sensor. Freewheeling integrates the Hall-rotation sensing and ProxFusion Channel 0 to detect deliberate flicks of a scroll wheel. On a flick, the Freewheel UI measures the rotational speed of the magnet, then continuously increments the Processed Angle at the measured rotational speed, as though the magnet was freely spinning. This speed will eventually decay until the freewheeling event has ended.

A freewheeling event can occur when the freewheeling UI is enabled, and a Movement Exit event occurs while the rotational speed of the physical input is greater than the *Freewheel Start Speed*. Freewheeling continues until the freewheeling speed decays below the value defined in the *Freewheel Stop Speed* parameter.

The movement release delta required to start a freewheeling event is defined by the *Forward Movement Threshold* and *Reverse Movement Threshold* parameters. These parameters are used to set different touch release sensitivity values for freewheeling in different directions.

Freewheeling can be manually stopped during the emulated rotation by triggering a touch event. The *Movement Stop Threshold* parameter will determine the delta of the Movement event required to stop freewheeling.

### 7.1 Effects of Freewheel Parameters

A simplified equation of the freewheeling angular velocity over time is displayed in Equation (6).

$$\omega_{n+1} = \omega_n - \frac{\text{Friction} + (\text{Damping} \times \omega_n)}{\text{Inertia}}.$$

(6)

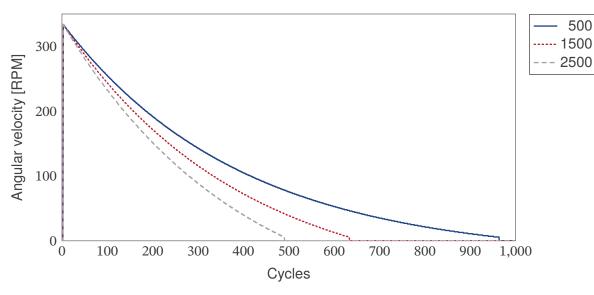

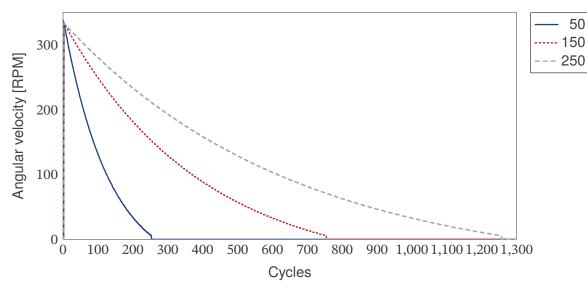

Figure 7.1 displays the change in angular velocity as the freewheeling friction parameter changes. Freewheeling damping remains constant with a value of 5000, and freewheeling inertia remains constant at 150.

Figure 7.1: Freewheel Response as Friction Changes

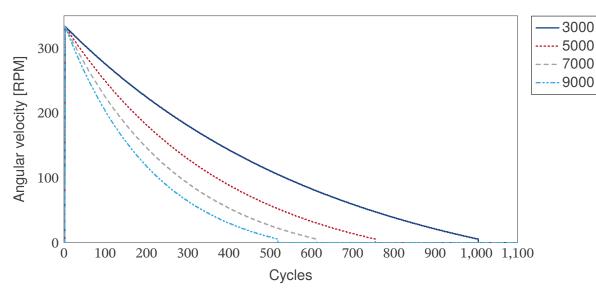

Figure 7.2 displays the change in angular velocity as the freewheeling damping parameter changes. Freewheeling friction remains constant with a value of 1000, and freewheeling inertia remains constant at 150.

Figure 7.2: Freewheel Response as Damping Changes

Figure 7.3 displays the change in angular velocity as the freewheeling inertia parameter changes. Freewheeling damping remains constant with a value of 5000, and freewheeling friction remains constant at 1000.

Figure 7.3: Freewheeling Response as Inertia Changes

## 7.2 Recommended Parameters

The freewheeling settings on the device all default to 0. The Table 7.1 provides recommended parameters to use as a starting point:

#### Table 7.1: Freewheeling Recommended Settings

| Parameter                      | Value |

|--------------------------------|-------|

| Decay Beta                     | 4     |

| Follow Beta                    | 2     |

| Freewheel Friction             | 20    |

| Freewheel Damping              | 5000  |

| Freewheel Inertia              | 180   |

| Freewheel Minimum Start Speed  | 40    |

| Freewheel Stop Speed           | 20    |

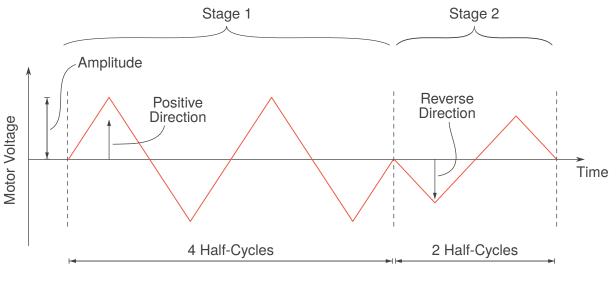

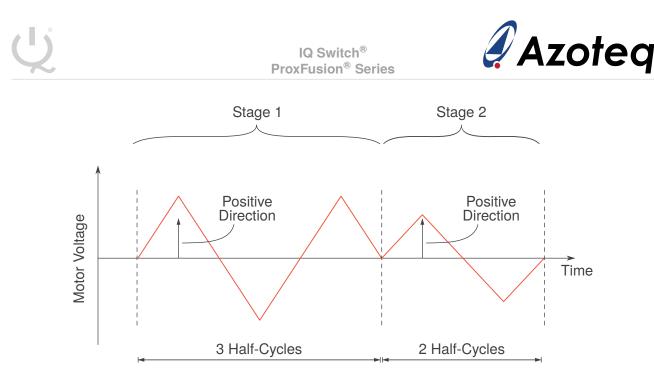

| CH0 Movement Stop Threshold    | 200   |